VerilogとVHDLの大きな違いは、VerilogがC言語をベースにしているのに対して、VHDLはAda言語やPascal言語をベースにしていることです。

VerilogとVHDLはどちらもハードウェア記述言語(HDL)です。

これらの言語は、マイクロプロセッサやフリップフロップなど、デジタルシステムのハードウェアを記述するのに役立ちます。

そのため、通常のプログラミング言語とは異なる。

VHDLは古い言語ですが、Verilogは最新の言語です。

Verilogとは

VerilogはHDL(Hardware Description Language)の一種です。

Verilogの最新安定版はIEEE1364-2005です。

Verilogは大文字と小文字を区別し、小文字のみを使用する言語です。

シミュレーションをサポートします。

つまり、実システムを構築する前に、機能のモデルを作成し、シミュレーションを行うことが可能である。

Verilogのベース言語はC言語であるため、C言語に慣れたプログラマはVerilogをすぐに習得することができる。

Verilogの基本的なビルディングブロックです。

入出力ポートの情報を提供し、内部実装の詳細を隠蔽します。

モジュールの構文は次のとおりです。

Verilogのプログラムは、moduleというキーワードで始まり、endmoduleというキーワードで終わります。

モジュール

endmodule

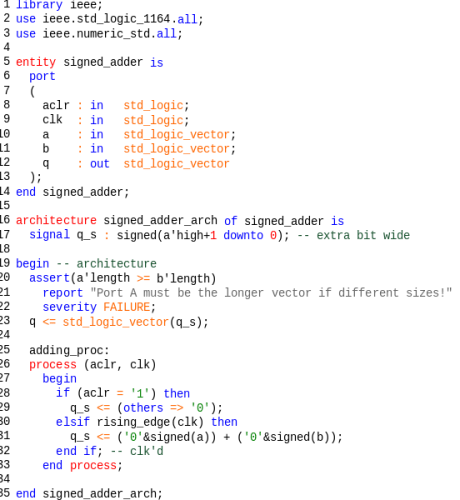

What is VHDL

VHDL is an HDL that helps to describe circuits in digital systems. A hardware module in VHDL is called an entity. The syntax is as follows. The entity starts with “entity” and ends with “end” keyword.

entity

port declaration;

end entity_name;

There are other keywords such as In, Out, Inout and Buffer. In represents the ports we can read. Out represents ports we can write. Inout represents ports we can read and write. Moreover, it is possible to read and write to a Buffer port, and it can only have one source.

There are main three types of modeling in VHDL. They are as follows.

Data flow modeling – Parallel signals represent the flow of data through an entity

Behavioral modeling – Represents the behavior of an entity as a set of statements to execute one after the other in a specified order

Structured modeling – Represents an entity as a set of interconnected components

Difference Between Verilog and VHDL

Definition

Verilog is an HDL used to model electronic systems while VHDL is an HDL used in electronic design automation to describe digital and mixed-signal systems such as field programmable gate arrays and integrated circuits.

Base Language

The main difference between Verilog and VHDL is that Verilog is based on C language while VHDL is based on Ada and Pascal languages.

Case Sensitive

Moreover, one other difference between Verilog and VHDL is that Verilog is case sensitive while VHDL is not case sensitive.

Introduced Time Period

Verilog is a newer language than VHDL as Verilog was introduced in 1984 while VHDL was introduced in 1980.

Complexity

Complexity is another difference between Verilog and VHDL. VHDL is complex than Verilog.

Conclusion

Verilog and VHDL are two Hardware Description Languages (HDL) that help to describe digital electronic systems. The main difference between Verilog and VHDL is that Verilog is based on C language while VHDL is based on Ada and Pascal languages.

_name>_name>